TSMC

Although TSMC can't claim to be the first fab to use extreme UV (EUV) lithography – that title goes to Samsung – they do get to claim to be the largest. As a result, the company has developed significant experience with EUV over the years, allowing TSMC to refine how they use EUV tooling to both improve productivity/uptime, and to cut down on the costs of using the ultra-fine tools. As part of the company's European Technology Symposium this week, they went into a bit more detail on their EUV usage history, and their progress on further integrating EUV into future process nodes. When TSMC started making chips using EUV lithography in 2019 on its N7+ process (for Huawei's HiSilicon), it held 42% of the...

TSMC to Expand Specialty Capacity by 50%, Introduce 4nm N4e Low-Power Node

With all the new fabs being built in Germany and Japan, as well as the expansion of production capacity in China, TSMC is planning to extend its production capacity...

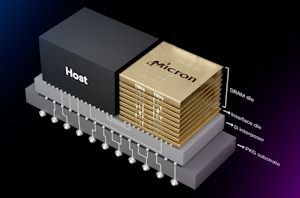

0 by Anton Shilov 2 days agoTSMC Readies Next-Gen HBM4 Base Dies, Built on 12nm and 5nm Nodes

Of the several major changes coming with HBM4 memory, one of the most immediate is the sheer width of the memory interface. With the fourth-generation memory standard moving from...

1 by Anton Shilov 3 days agoTSMC: Performance-Optimized 3nm N3P Process on Track for Mass Production This Year

As part of the second leg of TSMC's spring technology symposium series, the company offered an update on the state of its 3nm-class processes, both current and future. Building...

20 by Anton Shilov 3 days agoTSMC Readies 8x Reticle Super Carrier Interposer For Next-Gen Chips Twice as Large As Today's

TSMC is no stranger to building big chips. Besides the ~800mm2 reticle limit of their normal logic processes, the company already produces even larger chips by fitting multiple dies...

6 by Anton Shilov on 4/30/2024TSMC Jumps Into Silicon Photonics, Lays Out Roadmap For 12.8 Tbps COUPE On-Package Interconnect

Optical connectivity – and especially silicon photonics – is expected to become a crucial technology to enable connectivity for next-generation datacenters, particularly those designed HPC applications. With ever-increasing bandwidth...

9 by Anton Shilov on 4/26/2024TSMC Preps Cheaper 4nm N4C Process For 2025, Aiming For 8.5% Cost Reduction

While the bulk of attention on TSMC is aimed at its leading-edge nodes, such as N3E and N2, loads of chips will continue to be made using more mature...

5 by Anton Shilov on 4/25/2024TSMC 2nm Update: N2 In 2025, N2P Loses Backside Power, and NanoFlex Brings Optimal Cells

Taiwan Semiconductor Manufacturing Co. provided several important updates about its upcoming process technologies at its North American Technology Symposium 2024. At a high level, TSMC's 2 nm plans remain...

0 by Anton Shilov on 4/25/2024TSMC's 1.6nm Technology Announced for Late 2026: A16 with "Super Power Rail" Backside Power

With the arrival of spring comes showers, flowers, and in the technology industry, TSMC's annual technology symposium series. With customers spread all around the world, the Taiwanese pure play...

18 by Anton Shilov on 4/25/2024TSMC Posts Q1'24 Results: 3nm Revenue Share Drops Steeply, but HPC Share Rises

Taiwan Semiconductor Manufacturing Co. this week released its financial results for Q1 2024. Due to a rebound in demand for semiconductors, the company garned $18.87 billion in revenue for...

11 by Anton Shilov on 4/19/2024TSMC to Receive $6.6B Under US CHIPS Act, Set to Build 2nm Fab in Arizona

TSMC has entered into a preliminary agreement with the U.S. Department of Commerce, securing up to $6.6 billion in direct funding and access to up to $5 billion in...

23 by Anton Shilov on 4/8/2024NVIDIA's 'cuLitho' Computational Lithography Adopted By TSMC and Synopsys For Production Use

Last year, NVIDIA introduced its cuLitho software library, which promises to speed up photomask development by up to 40 times. Today, NVIDIA announced a partnership with TSMC and Synopsys...

21 by Anton Shilov on 3/18/2024Marvell's 2nm IP Platform Enables Custom Silicon for Datacenters

Marvell this week introduced its new IP technology platform specifically tailored for custom chips for accelerated infrastructure made on TSMC's 2nm-class process technologies (possibly including N2 and N2P). The...

0 by Anton Shilov on 3/8/2024ASML to Ship Multiple High-NA Tools in 2025, Expands Production Capacities

ASML began to ship its first High-NA lithography tool to Intel late last year ,and the machine will be fully assembled in Oregon in the coming months. Shipping only...

8 by Anton Shilov on 2/14/2024Global Semiconductor Sales Hit $526.8 Billion in 2023

The global semiconductor industry saw its sales dropped around $47 billion to nearly $527 billion in 2023, according to estimations by the Semiconductor Industry Association (SIA). This was a...

13 by Anton Shilov on 2/9/2024TSMC to Build Second Fab in Japan: 6nm and 7nm Coming to Japan

Taiwan Semiconductor Manufacturing Co. on Tuesday formally announced plans to build a second fab in Japan. The fab will be run by Japan Advanced Semiconductor Manufacturing (JASM), a majority-owned...

4 by Anton Shilov on 2/6/2024TSMC 2nm Update: Two Fabs in Construction, One Awaiting Government Approval

When Taiwan Semiconductor Manufacturing Co. (TSMC) is prepping to roll out an all-new process technology, it usually builds a new fab to meet demand of its alpha customers and...

38 by Anton Shilov on 1/19/2024TSMC Posts Q4'23 Earnings: 3nm Revenue Share Jumps to 15%, 5nm Overtakes 7nm For 2023

Taiwan Semiconductor Manufacturing Co. released its Q4'2023 and full year 2023 financial results this week. And along with a look at the financial state of the firm as it...

2 by Anton Shilov on 1/19/2024TSMC Solidifies Leadership on Foundry Market as Intel Jumps into Top 10

The global foundry industry witnessed a substantial rise in demand in the third quarter of 2023, according to TrendForce. The Top 10 foundries collectively saw their revenue soar to...

7 by Anton Shilov on 12/6/2023TSMC Q3 Earnings: 3nm Production Node Accounts for 6% of Revenue

Although Taiwan Semiconductor Manufacturing Co. formally started production of chips using its N3 (3nm-class) process technology back in late 2022, the company did not recognize any meaningful N3 revenue...

7 by Anton Shilov on 10/19/2023